We have some official data regarding AMD’s next-generation Ryzen 4000 CPU family which is based on the new refined Zen 3 core architecture. The information appears to be a part of some confidential AMD documents that were shared by CyberCatPunk, coming via Tom’s Hardware, and Wccftech.

The Zen 3 CPUs will be officially revealed on October 8, and now some specs have been leaked to give us some insights about the performance of these Zen 3-based CPUs. Likely to be fabbed on the TSMC’s 7nm+ EUV process node, the Zen 3 architecture is said to deliver better performance per watt ratio and efficiency than the previous Zen 2 lineup, which was already a revolutionary architecture from AMD.

As we already know the AMD Vermeer Desktop CPUs based on Zen 3 microarchitecture will be known as the AMD Family 19h Model 21h B0. According to these leaked official documents, Vermeer CPUs will be designed to be used in high-performance desktop platforms, and they are also going to feature up to two CCD’s (Core/Cache Complex Dies) and a single IOD (I/O Die). The document dates back to June 10.

The document appears to be a Processor Programming Reference (PPR) guide for AMD’s Family 19h Model 21h B0, which is Zen 3. For context, Zen+ and Zen 2 belong to Family 17h. As previous rumors have already pointed out, Ryzen 4000-series Vermeer processors will retain the multi-chip module (MCM) approach, the chiplet design. These leaked documents confirm the same as well.

Unlike the previous generation of AMD CPU lineup a single CCD housed two CCX’s (Core Complexes), however, in the case of Zen 3 CCD, a single CCX will feature up to 8 cores running either in a single-thread mode (1T) or a two-thread SMT (simultaneous multithreading) mode (2T), for up to 16 threads per CCX. The chip will have a maximum of two CCDs, so the core and thread count will max out to 16 cores and 32 threads only, same as the existing Ryzen 9 3950X desktop CPU. To reiterate, Zen 3 will have two core complex dies (CCDs) with a one I/O die (IOD) inside of a chip package.

According to the documents, there’s only one CCX inside each CCD. Since there’s only one CCX, all eight CPU cores can now directly access the 32MB of shared L3 cache. The amount of L3 cache remains the same at 32MB per CCD on Zen 3. This new revamped Zen 3 arch design will help lower latency, and also improve the overall instruction per cycle (IPC).

AMD will be introducing an improved scalable data fabric with Zen 3 cores with support up to 512 GB per DRAM channel or up to 1 TB of ECC DRAM. For the memory interface, these Ryzen 4000 Vermeer desktop CPUs will still have DDR4-3200 speeds. However, there will be 2 unified memory controllers on the CPU, and each of them will be supporting one DRAM channel for a total of 2 DIMMs per channel.

We hope Zen 3 architecture to bring at least 15-17% IPC uplift compared to the previous gen Zen 2 CPU lineup. Zen 2 CPUs already featured double the L3 cache over the Zen/Zen+ series chips, and ZEN 3 is going to take things to a whole new level.

AMD’s next-generation Zen 3 architecture aims to alleviate some of the shortcomings of AMD’s existing architecture designs. So, expect some AMD CPUs going as high as 5GHz, to give Intel a stiff competition on the single-core frequency, along with a 50% increase in Zen 3’s floating-point operations & a major cache redesign.

These are all the leaked specs from the documents as compiled by Wccftech.

Core Complex Die (CCD):

- Consists of one CCX

The CCX consists of:

- Up to 8 cores where each core may run in single-thread mode (1T) or two-thread SMT mode (2T)

for a total of up to 16 threads per complex - 512KB of L2 per core for a total of 4MB L2 per CCD

- Up to 32MB of L3 shared across all cores within the complex

Scalable Data Fabric. This provides the data path that connects the compute complexes, the I/O interfaces, and the memory interfaces to each other.

- Handles request, response, and data traffic

- Handles probe traffic to facilitate coherency, supporting up to 512GB per DRAM channel

- Handles interrupt request routing (APIC)

- Scalable Control Fabric. This provides the data path that provides a configuration access path to all blocks

- Handles configuration request, response, and data traffic

- GMI2: Up to two special Data Fabric ports, for connections to the CCDs.

Memory interface

- 2 Unified Memory Controllers (UMC), each supporting one DRAM channel

- 2 DDR4 PHYs. Each PHY supports:

- 64-bit data plus ECC

- 1 DRAM channel per PHY

- 2 DIMMs per channel

- DDR4 transfer rates from 1333MT/s to 3200MT/s

- UDIMM support

PSP and SMU

- MP0 (PSP) and MP1 (SMU) microcontrollers

- This document refers to the AMD Secure Processor technology as Platform Security Processor (PSP).

- Thermal monitoring

- Fuses

- Clock control

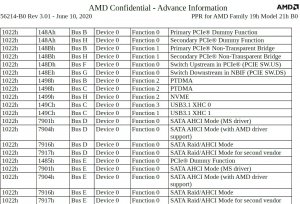

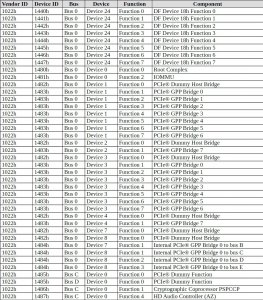

NBIO

- PCI Device ID information uses Vendor ID is 1022h for all devices (see Table 18 [PCI Device ID

]. - 2 SYSHUBs

- 1 IOHUB with IOMMU v2.x

- Two 8×16 PCIe controllers supporting Gen1/Gen2/Gen3/Gen4. Note that SATA Express is supported by combining an x2 PCIe® port and two SATA ports on the same 2 lanes.

- 24 total lanes combo PHY, UPI muxing

Fusion Controller Hub (FCH or southbridge (SB))

- ACPI

- CLKGEN/CGPLL for refclk generation

- GPIOs (varying number depending on muxing)

- LPC

- Real-Time Clock (RTC)

- SMBus

- SPI/eSPI

- Azalia

- High Definition Audio

- Up to 2 lanes of SATA Gen1/Gen2/Gen3, also provides the legacy SATA support for SATAe

- Shared with PCIe

- SGPIO

- 1 Gen2

- 4 ports, includes support for legacy USB speeds

AMD is expected to unveil its next-generation AM4 CPU lineup based on the Zen 3 core architecture on 8th October as confirmed before in an official announcement.

Stay tuned for more!

Hello, my name is NICK Richardson. I’m an avid PC and tech fan since the good old days of RIVA TNT2, and 3DFX interactive “Voodoo” gaming cards. I love playing mostly First-person shooters, and I’m a die-hard fan of this FPS genre, since the good ‘old Doom and Wolfenstein days.

MUSIC has always been my passion/roots, but I started gaming “casually” when I was young on Nvidia’s GeForce3 series of cards. I’m by no means an avid or a hardcore gamer though, but I just love stuff related to the PC, Games, and technology in general. I’ve been involved with many indie Metal bands worldwide, and have helped them promote their albums in record labels. I’m a very broad-minded down to earth guy. MUSIC is my inner expression, and soul.

Contact: Email